## Agilent HMPP-389x Series MiniPak Surface Mount RF PIN Switch Diodes

**Data Sheet**

## Description/Applications

These ultra-miniature products represent the blending of Agilent Technologies' proven semiconductor and the latest in leadless packaging technology.

The HMPP-389x series is optimized for switching applications where low resistance at low current and low capacitance are required. The MiniPak package offers reduced parasitics when compared to conventional leaded diodes, and lower thermal resistance.

Low junction capacitance of the PIN diode chip, combined with ultra low package parasitics, mean that these products may be used at frequencies which are higher than the upper limit for conventional PIN diodes.

Note that Agilent's manufacturing techniques assure that dice packaged in pairs are taken from adjacent sites on the wafer, assuring the highest degree of match.

The HMPP-389T low inductance wide band shunt switch is well suited for applications up to 6 GHz.

#### **Features**

- Surface mount MiniPak package

- low height, 0.7 mm (0.028") max.

- small footprint, 1.75 mm<sup>2</sup> (0.0028 inch<sup>2</sup>)

- Better thermal conductivity for higher power dissipation

- Single and dual versions

- Matched diodes for consistent performance

- Low capacitance

- · Low resistance at low current

- Low FIT (Failure in Time) rate\*

- Six-sigma quality level

- For more information, see the Surface Mount Schottky Reliability Data Sheet.

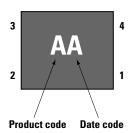

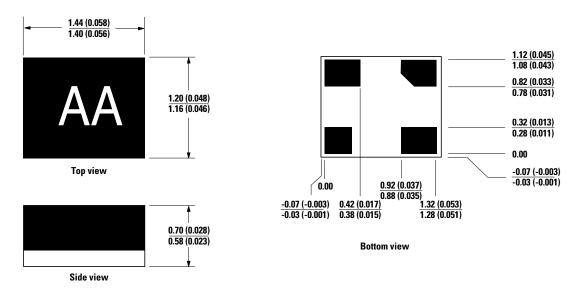

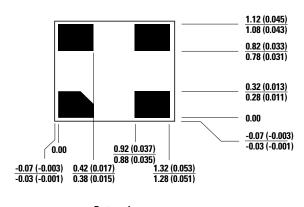

#### Pin Connections and Package Marking

#### Notes:

- 1. Package marking provides orientation and identification.

- See "Electrical Specifications" for appropriate package marking.

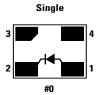

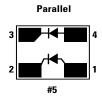

# Package Lead Code Identification (Top View)

### HMPP-389x Series Absolute Maximum Ratings [1], $T_{C}=25^{\circ}C$

| Symbol           | Parameter                         | Units | Value       |

|------------------|-----------------------------------|-------|-------------|

| I <sub>f</sub>   | Forward Current (1 µs pulse)      | Amp   | 1           |

| P <sub>IV</sub>  | Peak Inverse Voltage              | V     | 100         |

| T <sub>j</sub>   | Junction Temperature              | °C    | 150         |

| T <sub>stg</sub> | Storage Temperature               | °C    | -65 to +150 |

| $\theta_{jc}$    | Thermal Resistance <sup>[2]</sup> | °C/W  | 150         |

#### ESD WARNING: Handling Precautions Should Be Taken To Avoid Static Discharge.

#### Notes:

- Operation in excess of any one of these conditions may result in permanent damage to the device.

- 2.  $T_C = +25^{\circ}C$ , where  $T_C$  is defined to be the temperature at the package pins where contact is made to the circuit board.

## **Electrical Specifications,** $T_C = +25^{\circ}C$ , each diode

| Part Number<br>HMPP- | Package<br>Marking Code | Lead Code | Configuration | Minimum Breakdown<br>Voltage (V)                                   | $ \begin{array}{l} \text{Maximum Series} \\ \text{Resistance} \left(\Omega\right) \end{array}$ | Maximum Total<br>Capacitance (pF) |

|----------------------|-------------------------|-----------|---------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------|

| 3890                 | D                       | 0         | Single        | 100                                                                | 2.5                                                                                            | 0.30                              |

| 3892                 | С                       | 2         | Anti-parallel |                                                                    |                                                                                                |                                   |

| 3895                 | В                       | 5         | Parallel      |                                                                    |                                                                                                |                                   |

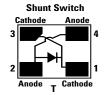

| 389T                 | T                       | T         | Shunt Switch  |                                                                    |                                                                                                |                                   |

| Test Condition       | ıs                      |           |               | V <sub>R</sub> = V <sub>BR</sub><br>Measure I <sub>R</sub> ≤ 10 μA | I <sub>F</sub> = 5 mA<br>f = 100 MHz                                                           | V <sub>R</sub> = 5 V<br>f = 1 MHz |

#### Typical Parameters, $T_C = +25^{\circ}C$

| Part Number<br>HMPP- | Series Resistance $R_S(\Omega)$      | Carrier Lifetime $	au$ (ns)                     | Total Capacitance<br>C <sub>T</sub> (pF) |  |

|----------------------|--------------------------------------|-------------------------------------------------|------------------------------------------|--|

| 389x                 | 3.8                                  | 200                                             | 0.20 @ 5 V                               |  |

| Test Conditions      | I <sub>F</sub> = 1 mA<br>f = 100 MHz | I <sub>F</sub> = 10 mA<br>I <sub>R</sub> = 6 mA |                                          |  |

#### **HMPP-389x Series Typical Performance,** $T_c = 25^{\circ}C$ , each diode

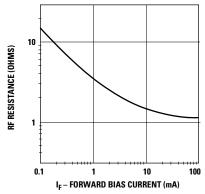

Figure 1. Total RF Resistance at 25°C vs. Forward Bias Current.

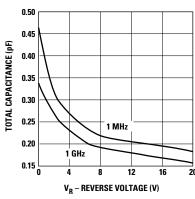

Figure 2. Capacitance vs. Reverse Voltage.

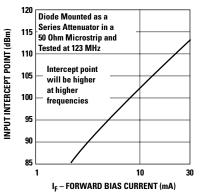

Figure 3. 2nd Harmonic Input Intercept Point vs. Forward Bias Current.

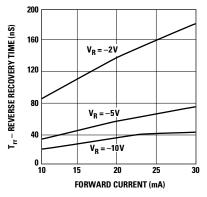

Figure 4. Typical Reverse Recovery Time vs. Reverse Voltage.

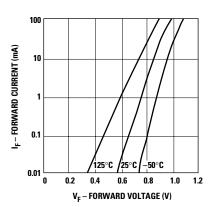

Figure 5. Forward Current vs. Forward Voltage.

#### **Typical Applications**

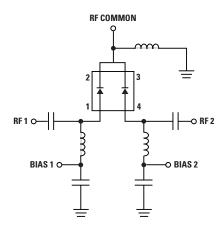

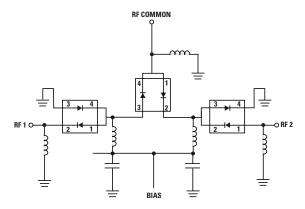

Figure 6. Simple SPDT Switch Using Only Positive Bias.

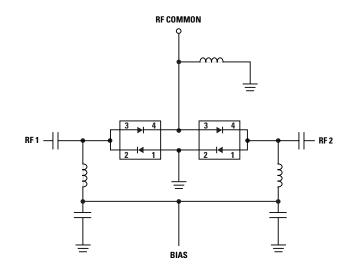

Figure 7. High Isolation SPDT Switch Using Dual Bias.

Figure 8. Very High Isolation SPDT Switch, Dual Bias.

# Applications Information PIN Diodes

In RF and microwave networks, mechanical switches and attenuators are bulky, often unreliable, and difficult to manufacture. Switch ICs, while convenient to use and low in cost in small quantities, suffer from poor distortion performance and are not as cost effective as PIN diode switches and attenuators in very large quantities. For over 30 years, designers have looked to the PIN diode for high performance/low cost solutions to their switching and level control needs.

In the RF and microwave ranges, the switch serves the simple purpose which is implied by its name; it operates between one of two modes, ON or OFF. In the ON state, the switch is designed to have the least possible loss. In the OFF state, the switch must exhibit a very high loss (isolation) to the input signal, typically from 20 to 60 dB. The attenuator, however, serves a more complex function. It provides for the "soft" or controlled variation in the power level of a RF or microwave signal. At the same time as it attenuates the input signal to some predetermined value, it must also present a matched input impedance (low VSWR) to the source. Every microwave network which uses PIN diodes (phase shifter, modulator, etc.) is a variation on one of these two basic circuits.

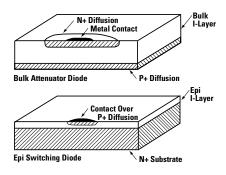

One can see that the switch and the attenuator are quite different in their function, and will therefore often require different characteristics in their PIN diodes. These properties are easily controlled through the way in which a PIN diode is fabricated. See Figure 9.

Figure 9. PIN Diode Construction.

#### **Diode Construction**

At Agilent Technologies, two basic methods of diode fabrication are used. In the case of bulk diodes, a wafer of very pure (intrinsic) silicon is heavily doped on the top and bottom faces to form P and N regions. The result is a diode with a very thick, very pure I region. The epitaxial layer (or EPI) diode starts as a wafer of heavily doped silicon (the P or N layer), onto which a thin I layer is grown. After the epitaxial growth, diffusion is used to add a heavily doped (N or P) layer on the top of the epi, creating a diode with a very thin I layer populated by a relatively large number of imperfections.

These two different methods of design result in two classes of diode with distinctly different characteristics, as shown in Table 1.

As we shall see in the following paragraphs, the bulk diode is almost always used for attenuator applications and sometimes as a switch, while the epi diode (such as the HMPP-3890) is generally used as a switching element.

#### **Diode Lifetime and Its Implications**

The resistance of a PIN diode is controlled by the conductivity (or resistivity) of the I layer. This conductivity is controlled by the density of the cloud of carriers (charges) in the I layer (which is, in turn, controlled by the DC bias). Minority carrier lifetime, indicated by the Greek symbol  $\tau$ , is a

Table 1. Bulk and EPI Diode Characteristics.

| Characteristic     | EPI Diode | Bulk Diode |  |

|--------------------|-----------|------------|--|

| Lifetime           | Short     | Long       |  |

| Distortion         | High      | Low        |  |

| Current Required   | Low       | High       |  |

| I Region Thickness | Very Thin | Thick      |  |

measure of the time it takes for the charge stored in the I layer to decay, when forward bias is replaced with reverse bias, to some predetermined value. This lifetime can be short (35 to 200 nsec. for epitaxial diodes) or it can be relatively long (400 to 3000 nsec. for bulk diodes). Lifetime has a strong influence over a number of PIN diode parameters, among which are distortion and basic diode behavior.

To study the effect of lifetime on diode behavior, we first define a cutoff frequency  $f_{\rm C}$  = 1/τ. For short lifetime diodes, this cutoff frequency can be as high as 30 MHz while for our longer lifetime diodes  $f_C \cong 400$  KHz. At frequencies which are ten times f<sub>C</sub> (or more), a PIN diode does indeed act like a current controlled variable resistor. At frequencies which are one tenth (or less) of  $f_C$ , a PIN diode acts like an ordinary PN junction diode. Finally, at  $0.1f_C \le f \le 10f_C$ , the behavior of the diode is very complex. Suffice it to mention that in this frequency range, the diode can exhibit very strong capacitive or inductive reactance—it will not behave at all like a resistor. However, at zero bias or under heavy forward bias, all PIN diodes demonstrate very high or very low impedance (respectively) no matter what their lifetime is.

#### **Diode Resistance vs. Forward Bias**

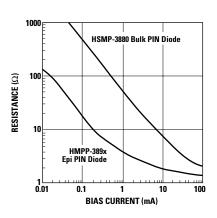

If we look at the typical curves for resistance vs. forward current for bulk and epi diodes (see Figure 10), we see that they are very different. Of course, these curves apply only at frequencies >  $10~\rm f_C$ . One can see that the curve of resistance vs. bias current for the bulk diode is much higher than that for the epi (switching) diode.

Thus, for a given current and junction capacitance, the epi diode will always have a lower resistance than the bulk diode. The thin epi diode, with its physically small I region, can easily be saturated (taken to the point of minimum resistance) with very little current compared to the much larger bulk diode. While an epi diode is well saturated at currents around 10 mA, the bulk diode may require upwards of 100 mA or more. Moreover, epi diodes can achieve reasonable values of resistance at currents of 1 mA or less, making them ideal for battery operated applications. Having compared the two basic types of PIN diode, we will now focus on the HMPP-3890 epi diode.

Given a thin epitaxial I region, the diode designer can trade off the device's total resistance  $(R_{\rm S}+R_{\rm j})$  and junction capacitance  $(C_{\rm j})$  by varying the diameter of the contact and I region. The HMPP-3890 was designed with the 930 MHz cellular and RFID, the 1.8 GHz PCS and 2.45 GHz RFID markets in mind. Combining the low resistance shown in Figure 10 with a typical total capacitance of 0.27 pF, it forms the basis for high performance, low cost switching networks.

Figure 10. Resistance vs, Forward Bias.

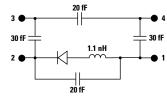

#### **Linear Equivalent Circuit**

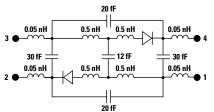

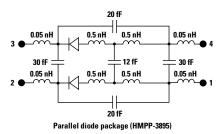

In order to predict the performance of the HMPP-3890 as a switch, it is necessary to construct a model which can then be used in one of the several linear analysis programs presently on the market. Such a model is given in Figure 11, where  $R_S + R_i$  is given in Figure 1 and C<sub>i</sub> is provided in Figure 2. Careful examination of Figure 11 will reveal the fact that the package parasitics (inductance and capacitance) are much lower for the MiniPak than they are for leaded plastic packages such as the SOT-23, SOT-323 or others. This will permit the HMPP-389x family to be used at higher frequencies than its conventional leaded counterparts.

Single diode package (HMPP-3890)

Anti-parallel diode package (HMPP-3892)

Figure 11. Linear Equivalent Circuit of the MiniPak PIN Diode.

## Testing the HMPP-389T on the Demo-board

#### Introduction

The HMPP-389T PIN diode is a high frequency shunt switch. It has been designed as a smaller and higher performance version of the HSMP-389T (SC-70 package).

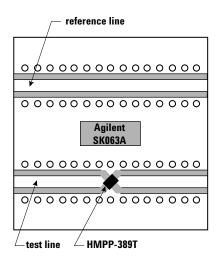

The DEMO-HMPP-389T demoboard allows customers to evaluate the performance of the HMPP-389T without having to fabricate their own PCB. Since a shunt switch's isolation is limited primarily by its parasitic inductance, the product's true potential cannot be shown if a conventional microstrip pcb is used. In order to overcome this problem, a coplanar waveguide over ground-plane structure is used for the demoboard. The bottom ground-plane is connected to the upper ground traces using multiple via-holes.

A  $50\Omega$  reference line is provided at the top to calibrate the board loss. The bottom line allows the HMPP-389T diode to be tested as a shunt switch.

Figure 12. Demo-board DEMO-HMPP-389T.

#### **Demo-board Preparation**

Since the performance of the shunt switch is ultimately limited by the demo-board, a short discussion of the constructional aspects will be beneficial. Edgemounted SMA connectors (Johnson #142-0701-881) were mounted on both the reference and test lines. A special mounting technique has been used to minimize reflection at the pcb to connector interface. Prior to mounting, the connector pins were cut down to two pin diameters in length. Subsequently, the connector fingers were soldered to the upper ground plane (Figure 13). Solder was filled between the connector body and fingers on the lower ground plane until the small crescent of exposed teflon was completely covered (Figure 14).

Figure 13. Soldering details of connector fingers to upper ground plane.

Figure 14. Soldering details of connector fingers to lower ground plane.

#### **Test Results**

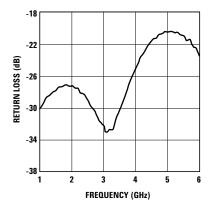

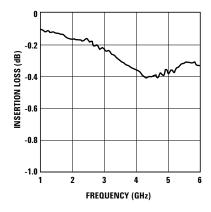

Measurements of the reference line's return and insertion losses were used to gauge the effectiveness of the VSWR mitigating steps. In our prototype, the worst case return loss of the reference line was 20 dB at 5 GHz (Figure 15).

Figure 15. Swept return loss of reference line.

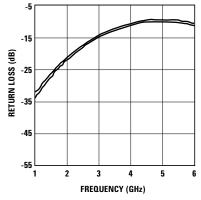

Insertion loss of the reference was very low and generally, increased with frequency (Figure 16). If the demo-board has been constructed carefully, there should not be any evidence of resonance. The reference line's insertion loss trace can be stored in the VNA's display memory and used to correct for the insertion loss of the test line in the subsequent measurements.

Figure 16. Insertion loss of reference line.

To evaluate the HMPP-389T as shunt switch, it was mounted on the test line and then the appropriate biasing voltage was applied. In our prototype, the worst case return loss was 10 dB at 5 GHz (Figure 17). The return loss varied very little when the bias was changed from zero to -20V.

Figure 17. Return loss of HMPP-389T mounted on test line at OV and -20V bias.

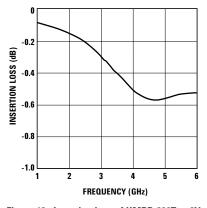

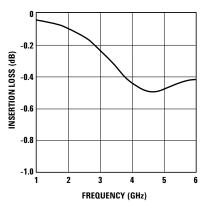

Normalization was used to remove the pcb's and connectors' losses from the measurement of the shunt switch's loss. The active trace was divided by the memorized trace (Data/Memory) to produce the normalized data. At zero bias, the insertion loss was under 0.6 dB up to 6 GHz (Figure 18). Applying a reverse bias to the PIN diode has the effect of reducing its parasitic capacitance. With a reverse bias of -20V, the insertion loss improved to better than 0.5 dB (Figure 19).

Figure 18. Insertion loss of HMPP-389T at 0V.

Figure 19. Insertion loss of HMPP-389T at -20V.

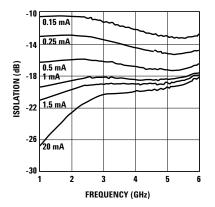

The PIN diode's resistance is a function of the bias current. So, at higher forward current, the isolation improved. The combination of the HMPP-389T and the SK063A demoboard exhibited more than 17 dB of isolation from 1 to 6 GHz at If  $\geq$  1mA (Figure 20).

Figure 20. Isolation at different frequencies with forward current as a parameter.

The combination of the HMPP-389T and the demo-board allows a high performance shunt switch to be constructed swiftly and economically. The extremely low parasitic inductance of the package allows the switch to operate over a very wide frequency range.

#### **Assembly Information**

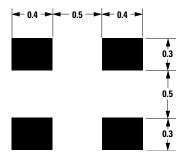

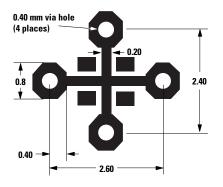

The MiniPak diode is mounted to the PCB or microstrip board using the pad pattern shown in Figure 21.

Figure 21. PCB Pad Layout, MiniPak (dimensions in mm).

This mounting pad pattern is satisfactory for most applications. However, there are applications where a high degree of isolation is required between one diode and the other is required. For such applications, the mounting pad pattern of Figure 22 is recommended.

Figure 22. PCB Pad Layout, High Isolation MiniPak (dimensions in mm).

This pattern uses four via holes, connecting the crossed ground strip pattern to the ground plane of the board.

#### **SMT** Assembly

Reliable assembly of surface mount components is a complex process that involves many material, process, and equipment factors, including: method of heating (e.g., IR or vapor phase reflow, wave soldering, etc.) circuit board material, conductor thickness and pattern, type of solder alloy, and the thermal conductivity and thermal mass of components. Components with a low mass, such as the MiniPak package, will reach solder reflow temperatures faster than those with a greater mass.

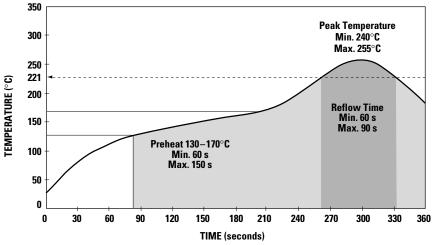

Agilent's diodes have been qualified to the time-temperature profile shown in Figure 23. This profile is representative of an IR reflow type of surface mount assembly process.

After ramping up from room temperature, the circuit board with components attached to it (held in place with solder paste) passes through one or more preheat zones. The preheat zones increase the temperature of the board and components to prevent thermal shock and begin evaporating solvents from the solder paste. The reflow zone briefly elevates the temperature sufficiently to produce a reflow of the solder.

The rates of change of temperature for the ramp-up and cooldown zones are chosen to be low enough to not cause deformation of the board or damage to components due to thermal shock. The maximum temperature in the reflow zone ( $T_{\rm MAX}$ ) should not exceed 255°C.

These parameters are typical for a surface mount assembly process for Agilent diodes. As a general guideline, the circuit board and components should be exposed only to the minimum temperatures and times necessary to achieve a uniform reflow of solder.

Figure 23. Surface Mount Assembly Temperature Profile.

#### MiniPak Outline Drawing for HMPP-3890, -3892, and -3895

#### MiniPak Outline Drawing for HMPP-389T

Bottom view

Dimensions are in millimeteres (inches)

#### **Ordering Information**

| Part Number   | No. of Devices | Container      |

|---------------|----------------|----------------|

| HMPP-389x-TR2 | 10000          | 13" Reel       |

| HMPP-389x-TR1 | 3000           | 7"Reel         |

| HMPP-389x-BLK | 100            | antistatic bag |

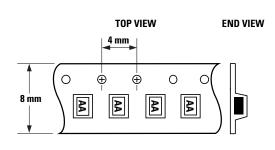

#### **Device Orientation**

Note: "AA" represents package marking code. Package marking is right side up with carrier tape perforations at top. Conforms to Electronic Industries RS-481, "Taping of Surface Mounted Components for Automated Placement." Standard quantity is 3,000 devices per reel.

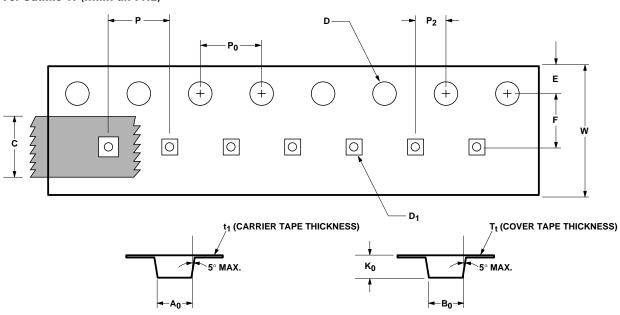

# Tape Dimensions and Product Orientation For Outline 4T (MiniPak 1412)

| DESCRIPTION  |                                          | SYMBOL         | SIZE (mm)                         | SIZE (INCHES)                         |

|--------------|------------------------------------------|----------------|-----------------------------------|---------------------------------------|

| CAVITY       | LENGTH                                   | A <sub>0</sub> | 1.40 ± 0.05                       | $0.055 \pm 0.002$                     |

|              | WIDTH                                    | B <sub>0</sub> | $1.63 \pm 0.05$                   | $\textbf{0.064} \pm \textbf{0.002}$   |

|              | DEPTH                                    | K <sub>0</sub> | $\textbf{0.80} \pm \textbf{0.05}$ | $0.031 \pm 0.002$                     |

|              | PITCH                                    | P              | $4.00 \pm 0.10$                   | $0.157 \pm 0.004$                     |

|              | BOTTOM HOLE DIAMETER                     | D <sub>1</sub> | $0.80 \pm 0.05$                   | $0.031 \pm 0.002$                     |

| PERFORATION  | DIAMETER                                 | D              | 1.50 ± 0.10                       | 0.060 ± 0.004                         |

|              | PITCH                                    | P <sub>0</sub> | $4.00 \pm 0.10$                   | $0.157 \pm 0.004$                     |

|              | POSITION                                 | E              | 1.75 ± 0.10                       | $\textbf{0.069} \pm \textbf{0.004}$   |

| CARRIER TAPE | WIDTH                                    | w              | 8.00 + 0.30 - 0.10                | 0.315 + 0.012 - 0.004                 |

|              | THICKNESS                                | t <sub>1</sub> | $0.254 \pm 0.02$                  | $0.010 \pm 0.001$                     |

| COVER TAPE   | WIDTH                                    | С              | 5.40 ± 0.10                       | 0.213 ± 0.004                         |

|              | TAPE THICKNESS                           | Tt             | $0.062 \pm 0.001$                 | $\textbf{0.002} \pm \textbf{0.00004}$ |

| DISTANCE     | CAVITY TO PERFORATION (WIDTH DIRECTION)  | F              | $3.50\pm0.05$                     | 0.138 ± 0.002                         |

|              | CAVITY TO PERFORATION (LENGTH DIRECTION) | P <sub>2</sub> | $\textbf{2.00} \pm \textbf{0.05}$ | $0.079 \pm 0.002$                     |

#### www.agilent.com/semiconductors

For product information and a complete list of distributors, please go to our web site.

For technical assistance call:

Americas/Canada: +1 (800) 235-0312 or

(408) 654-8675

Europe: +49 (0) 6441 92460 China: 10800 650 0017 Hong Kong: (+65) 271 2451

India, Australia, New Zealand: (+65) 271 2394

Japan: (+81 3) 3335-8152(Domestic/International), or

0120-61-1280(Domestic Only) Korea: (+65) 271 2194

Malaysia, Singapore: (+65) 271 2054

Taiwan: (+65) 271 2654

Data subject to change.

Copyright © 2002 Agilent Technologies, Inc.

Obsoletes 5988-4071EN

February 20, 2002

5988-5733EN