# Protection of Lithium Ion/Lithium Polymer Battery(one cell) Monolithic IC MM3077

### Outline

This protection IC was developed for use with lithium-ion/lithium polymer secondary 1-cell serial batteries. It detects overcharge, overdischarge, discharge overcurrent and other abnormalities, and functions to protect the battery by turning off the external FET-SW.

The IC also has a built-in timer circuit (for detection delay times), so fewer external parts can be used in protection circuit configuration.

#### **Features**

|   | (1) High withstand voltage CMOS process used          | Charger connection absolute maximum rating 28V                                |  |  |  |  |

|---|-------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

|   | (2) High electrostatic tolerance                      | 20kV (150pF, 330 $\Omega$ aerial, contact discharge)                          |  |  |  |  |

|   | (3) Detection voltage precision                       | Overcharge detection precision $\pm 25 \text{mV} (0 \sim 50^{\circ}\text{C})$ |  |  |  |  |

|   |                                                       | Discharge overcurrent detection precision ±10mV                               |  |  |  |  |

|   |                                                       | Overdischarge detection precision ±58mV                                       |  |  |  |  |

|   | (4) Built-in detection delay time (timer circuit)     | Overcharge detection delay time 0.25 ~ 7.0s (mask option)                     |  |  |  |  |

|   |                                                       | Overdischarge detection delay time 4.0 ~ 32.0ms (mask option)                 |  |  |  |  |

|   |                                                       | Discharge overcurrent detection delay time 4.0 ~ 32.0ms (mask option)         |  |  |  |  |

|   |                                                       | Short detection delay time 400µs                                              |  |  |  |  |

|   | (5) Includes detection function for too large charger | Detection voltage for too large charger 8.0V                                  |  |  |  |  |

| ( | 6) Setting DS pin                                     | At VDD level allows shortening of overcharge, excess discharge,               |  |  |  |  |

|   |                                                       | discharge overcurrent detection and reset delay time.                         |  |  |  |  |

|   | (7) OV observing prohibition function (mark option)   |                                                                               |  |  |  |  |

(7) OV charging prohibition function (mask option)

### Package

SOT-26 SON-6

### **Applications**

Lithium-ion/lithium polymer battery protection circuits

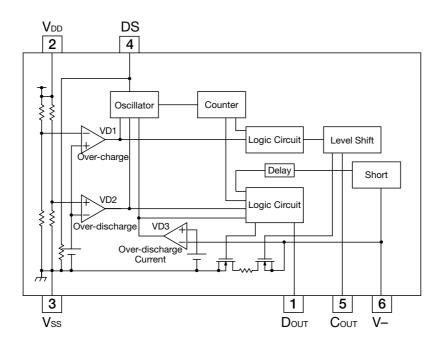

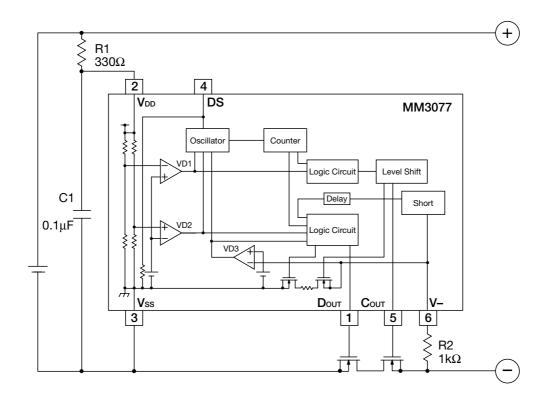

# Block diagram

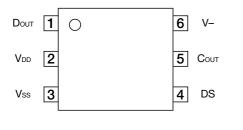

# **Pin Assignment**

| 1 | Dout |  |  |

|---|------|--|--|

| 2 | Vdd  |  |  |

| 3 | Vss  |  |  |

| 4 | DS   |  |  |

| 5 | Cout |  |  |

| 6 | V–   |  |  |

# **Pin Description**

| Pin No. | Pin Name | Function                                              |  |

|---------|----------|-------------------------------------------------------|--|

| 1       | Dout     | Over discharge detection Output. Output type is CMOS. |  |

| 2       | VDD      | VDD terminal. Connected to IC substrait.              |  |

| 3       | Vss      | Vss terminal. Connected to IC ground.                 |  |

| 4       | DS       | Delay shorten terminal.                               |  |

| 5       | Cout     | Over charge detection Output. Output type is CMOS.    |  |

| 6       | V–       | Charger negative voltage input.                       |  |

# Absolute maximum ratings (Topr=25°C, Vss=0V)

| Item                            | Symbol          | Rating                       | Unit |  |

|---------------------------------|-----------------|------------------------------|------|--|

| Supply voltage                  | V <sub>DD</sub> | -0.3 ~ 12                    | V    |  |

| Charger minus pin input voltage | V-              | $V_{DD}$ -28 ~ $V_{DD}$ +0.3 | V    |  |

| DS pin input voltage            | VDS             | Vss-0.3 ~ Vdd+0.3            | V    |  |

| Cout pin output voltage         | VCout           | $V_{DD}$ -28 ~ $V_{DD}$ +0.3 | V    |  |

| Dout pin output voltage         | VDout           | Vss-0.3 ~ Vdd+0.3            | V    |  |

| Operating temperature           | Topr            | -40 ~ +85                    | °C   |  |

| Storage temperature             | Tstg            | -55 ~ +125                   | °C   |  |

# Electrical characteristics (TOPR=25°C)

| Parameter                                  | Symbol | Conditions                            | min.    | typ.    | max.    | Unit | *2 |

|--------------------------------------------|--------|---------------------------------------|---------|---------|---------|------|----|

| Operating input voltage                    | VDD1   | VDD-Vss                               | 1.5     |         | 10.0    | V    | Α  |

| Minimum operating voltage for 0V charging  | Vst    | VDD-V-, VDD-VSS=0V                    |         |         | 1.2     | V    | A  |

| Over-charge detection voltage              | VDET1  | R1=330Ω Topr=0 ~ 50°C, *1             | 4.275   | 4.300   | 4.325   | V    | В  |

| Over-charge detection delay time           | tVdet1 | $V_{DD}=3.6V\rightarrow4.4V$          | 0.7     | 1.0     | 1.3     | S    | В  |

| Over-charge release voltage                | VREL1  | R1=330Ω                               | 4.050   | 4.100   | 4.150   | V    | В  |

| Over-charge release delay time             | tVrel1 | VDD=4.4V→3.6V                         | 5.6     | 8.0     | 10.4    | ms   | В  |

| Over-discharge detection voltage           | VDET2  | Detect falling edge of supply voltage | 2.242   | 2.300   | 2.358   | V    | D  |

| Over-discharge detection delay time        | tVdet2 | VDD=3.6V→2.2V                         | 16.8    | 24.0    | 31.2    | ms   | D  |

| Over-discharge release delay time          | tVrel2 | $V_{DD}=3V, V==3V \rightarrow 0V$     | 2.8     | 4.0     | 5.2     | ms   | Е  |

| Over-discharge current detection voltage   | VDET3  | Detect falling edge of supply voltage | 0.140   | 0.150   | 0.160   | V    | F  |

| Over-discharge curent detection delay time | tVdet3 | VDD=3V, V== $0V \rightarrow 1V$       | 8.4     | 12.0    | 15.6    | ms   | F  |

| Over-discharge current release delay time  | tVrel3 | V <sub>DD</sub> =3V, V−=3V→0V         | 2.8     | 4.0     | 5.2     | ms   | F  |

| Short detection voltage                    | VSHORT | VDD=3V                                | VDD-1.2 | VDD-0.9 | VDD-0.6 | V    | F  |

| Short detection delay time                 | tshort | VDD=3V, V== $0V \rightarrow 3V$       | 250     | 400     | 600     | μs   | F  |

| Over-discharge current release resistance  | RSHORT | VDD=3.6V, V-=1V                       | 30      | 50      | 100     | kΩ   | F  |

| DS pin "H"input voltage                    | VIH    |                                       | VDD-0.5 |         | VDD+0.3 | V    | Η  |

| DS pin pull-down resistance                | Rds    | $V_{DD}=3.6V$                         | 6.5     | 13.0    | 26.0    | kΩ   | Η  |

| Cout pin Nch ON voltage                    | Vol1   | IOL= $50\mu A$ , VDD= $4.5V$          |         | 0.4     | 0.5     | V    | Ι  |

| Cout pin Pch ON voltage                    | Voh1   | Іон=50µА, Vdd=3.9V                    | 3.4     | 3.7     |         | V    | J  |

| Dout pin Nch ON voltage                    | Vol2   | IOL=50 $\mu$ A, VDD=2.0V              |         | 0.2     | 0.5     | V    | Κ  |

| Dout pin Pch ON voltage                    | VDD2   | IDD=50µA, VDD=3.9V                    | 3.4     | 3.7     |         | V    | L  |

| Current consumption                        | Idd    | VDD=3.9V, V-=0V                       |         | 3.0     | 6.0     | μA   | Μ  |

| Current consumption at stand-by            | Is     | $V_{DD}=2.0V$                         |         |         | 0.1     | μA   | Μ  |

| Over voltage charger detection voltage     | VCHG1  | $V_{DD}=3.6V$                         | 6.0     | 8.0     | 10.0    | V    | G  |

| Over voltage charger release voltage       | VCHG2  | $V_{DD}=3.6V$                         | 5.3     | 7.3     | 9.3     | V    | G  |

\*1 The parameter is guaranteed by desing.

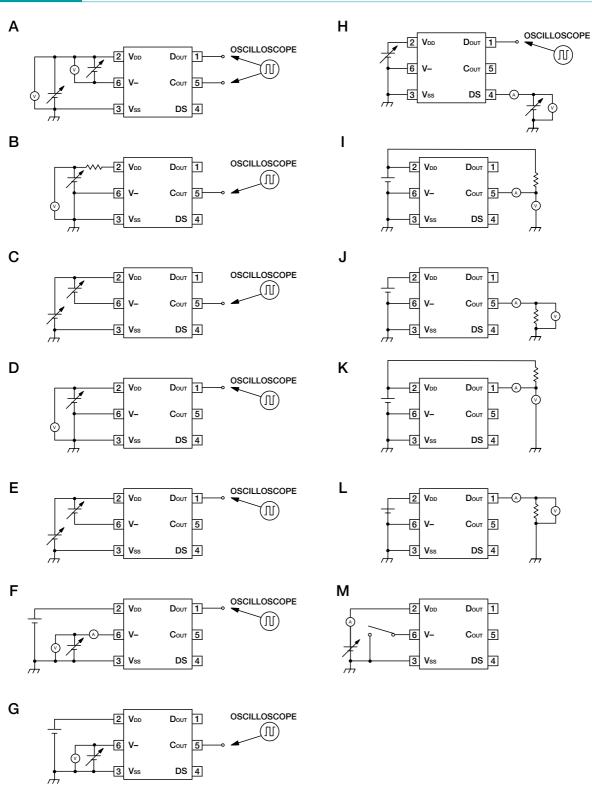

\*2 The test circuit symbols on next page.

### Test circuit

### Description

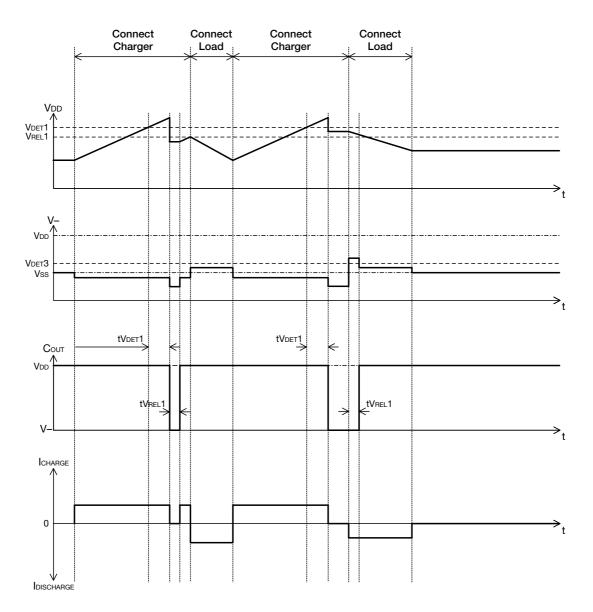

#### 1. Over charge detection circuit (VD1)

This IC monitor V<sub>DD</sub> pin voltage, when the voltage of V<sub>DD</sub> pin cross overcharge detection voltage (4.30V typ.) from a low value higher than the overcharge detection voltage, the IC sense a overcharging and external charging control Nch MOS FET turns to OFF with Cout pin being low level.

After detecting overcharge when the VDD pin voltage is coming down to a level lower than overcharge release voltage (4.10V typ.) external charging control Nch MOS FET turns to ON with COUT pin being high level.

After detecting overcharge in the V<sub>DD</sub> pin voltage, connecting system load to the battery charger makes load current allowable supplied to parasitic diode of charging control FET. The C<sub>OUT</sub> pin level would be high when the V<sub>DD</sub> pin level is coming down to a level below the overcharge detection voltage by continuous sending a load current.

There are delay time set in IC when the overcharge and the overcharge release are detected. When the V<sub>DD</sub> level is going up to a higher level than overcharge detection voltage if the V<sub>DD</sub> voltage would be back to a level lower than the overcharge detection voltage within a time period of the over charge release delay time (1.0s typ.). The overcharge detection does not release when returning to former state in the overcharge release dead time (8ms typ.) even if the load is connected after the charger is removed when the V<sub>DD</sub> pin voltage is lower than the overcharge release voltage with the overcharge detected.

A level shifter incorporated in a buffer drive for the Cout to the V-pin voltage and the high level of Cout is set to VDD voltage with CMOS buffer.

#### 2. Over discharge detection circuit (VD2)

This IC monitors V<sub>DD</sub> pin voltage, and when the voltage crosses the overdischarge detection voltage (2.30V typ.) from high value to a value lower than the overdischarge detection voltage, this IC sense an overdischarge and an external discharging control Nch MOS FET turns to OFF with Dout pin being at low level.

The release from the overdischarge is done only by connecting the charger. Charging current is supplied through a parasitic diode of Nch MOS FET when the VDD pin voltage is below the overdischarge detection voltage to the connection of the charger, and the DOUT pin enters the state which can be discharged by becoming high level, and turning on Nch MOS FET when the VDD pin voltage rises more than the overdischarge detection voltage.

The Cout pin becomes high level and charging current is supplied if the voltage of the charger is more than the maximum value of 0V charging lowest operating voltage when the voltage of the battery is 0V.

An output delay time for the overdischarge detection is fixed internally (8ms typ.). When V<sub>DD</sub> pin voltage becomes lower the over discharge detection voltage if V<sub>DD</sub> pin higher more than the over discharge detection voltage in delay time even does not enter the over discharge detection mode. Moreover, when the over discharge release, delay time is set (4ms typ.).

All the circuits are stopped, and after the overdischarge is detected, it is assumed the state of the standby, and decreases the current (standby current) which IC consumes as much as possible (The  $V_{DD} = 2V 0.1 \mu A$  max.).

The output type of  $D_{OUT}$  pin is CMOS having high level of  $V_{DD}$  and low level of Vss .

#### 3. Discharging over current detector, Short detector (VD3, Short Detector)

When the V-pin voltage is going up to a value during the short detection voltage (V<sub>DD</sub>-0.9V typ.) and overdischarge current detection voltage (0.150V typ.) is overdischarge current detection mode, when the V-pin voltage higher than short detection voltage makes the short detection mode. This leads the external discharge control Nch MOS FET turns to OFF with the Dout pin being at low level.

An output delay time for the overdischarge current detection is fixed internally (12ms typ.). When V-pin voltage becomes during the over discharge current detection voltage and the short circuit detection if V-pin lowers more than the over discharge current detection voltage in delay time even does not enter the over discharge current detection mode. Moreover, when the over discharge current release, delay time is set (4ms typ.).

The delay time set in IC exists when the short circuit is detected (400µs typ.).

The over discharge current release resistance ( $100k\Omega$  typ.) is built into between V-pin and Vss pin. When the load opened after detecting the over discharge current or the short circuit, V-pin is pulled down to the Vss through the over discharge current release resistance, And IC returns automatically from the over discharge current or the short circuit detection mode when V-pin voltage becomes below the over discharge current detection voltage. When the over discharge current or the short circuit is detected, the over discharge current release resistance is turned on. The over discharge current release resistance is usually turned off.

#### 4. DS (Delay Shortening)function

The overcharge, the over discharge, the over discharge current detection, and the delay time when returning can be shortened by impressing the  $V_{DD}$  voltage level to the terminal DS.

In the DS pin, the pull-down resistance of  $13 \text{k}\Omega$  is connected between Vss.

Please connect Vss or open the DS pin when using usually.

### **Application Circuit**

#### Application hints

R1 and C1 stabilize a supply voltage to the MM3077. However, the detection voltage rises by the current of penetration in IC of the voltage detection when R1 is enlarged, and the value of R1 is adjusted to  $1k\Omega$  or less. Moreover, please adjust the value of C1 to  $0.01\mu$ F or more to do the stability operation.

R1 and R2 are current limit resistance if a charger is connected reversibly or a high-voltage charger that exceed the absolute maximum rating is connected. R1 and R2 may cause a power consumption will be over rating of power dissipation therefore the `R1+R2` should be more than  $1k\Omega$ . Moreover, the charger connection release after the overedischarge is detected cannot be occasionally done when R2 is enlarged, and adjust the value of R2 to  $10k\Omega$  or less, please.

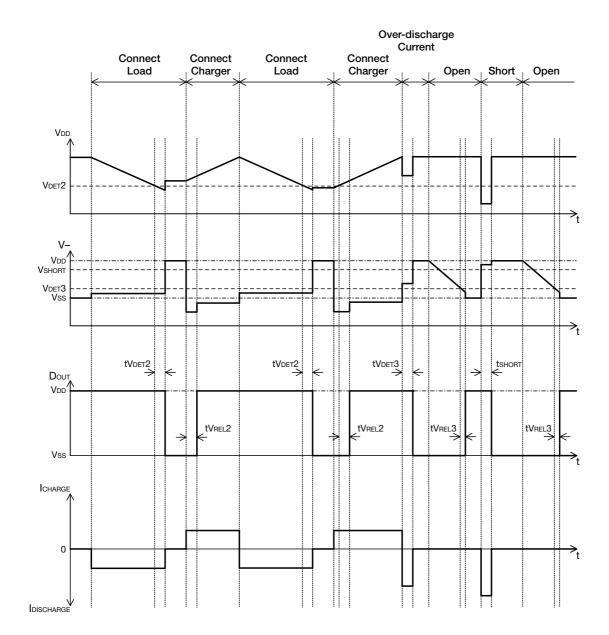

# **Timing chart**

1 Over-charge operations

### **Timing chart**

Over-discharge, over-discharge current, short operations